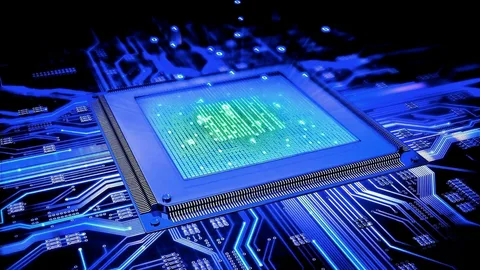

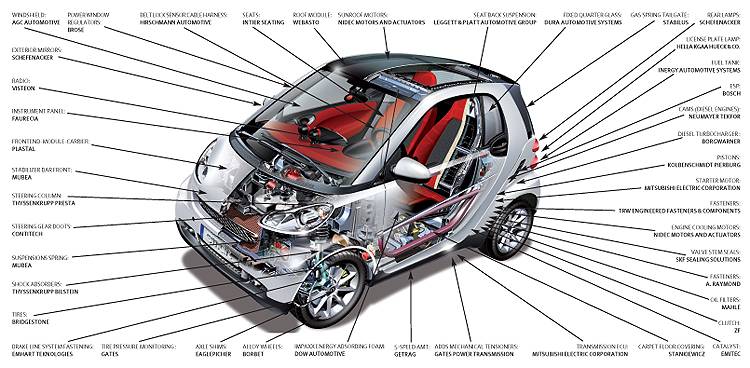

Designing digital circuits and systems requires the use of two primary hardware description languages called VHDL and Verilog. These languages are the fundamental tools that help to create and simulate digital circuits. Depending upon the project requirements team expertise and design complexity, the use of language is decided. Each hardware description language has its unique features and advantages. Verilog and VHDL hardware description languages are used in VLSI designing for digital circuits. The use of vlsi chips helps to integrate circuits by stimulating and creating them. Both Verilog and VDHL play a prominent role in designing VLSI. Verilog is often preferred for its simplicity and ease of use as it is ideal for projects that require fast development cycles and are more hardware-centric. Contrary to this, VHDL is preferred for industries where rigorous design specifications and detailed documentation are critical. These are generally industries related to aerospace or defence applications. VDHL syntax is more complicated and offers better control over design. However, it takes longer to develop due to this complexity. While both description languages for hardware have their pros and cons, they both are essential for modern VSLI design. Let us look at a comparative view to analyze the advantages and disadvantages of both languages:

- Verilog and VDHL: Verilog and VDHL are languages used to model digital systems at different levels of abstraction varying from the algorithm to the gate level. This allows the designers to describe the behaviour and structure of hardware circuits. These can further be synthesized into physical circuits or simulated for validation. Verilog is a hardware description language used for designing and simulating digital systems. It is used for synthesizing digital systems and the syntax is similar to the C programming language. This makes it easier to learn and use, especially for engineers with a background in software programming. VDHL is used to describe the behaviour of Very High-Speed Integrated Circuits or VHSIC and is more verbose and strongly typed. It is suitable for large-scale systems that are more complex.

- Syntactical differences between Verilog and VDHL: Verilog is known for its C programming-like syntax and is compact. This makes it easy to learn, for those familiar with programming languages. It is written quickly due to its succinct style, especially for smaller designs. VDHL has a syntax similar to Pascal or Ada. It is more challenging for beginners due to its strict type-checking. It is useful in creating highly structured complex designs and adding more detailed specifications to a system’s behaviour. With integrated chip design the working of the systems becomes fast and quicker.

- Ease of learning and use: As stated previously, Verilog is considered easy for individuals with a programming background in software development. It is chosen in markets where time-to-market is critical. This makes it ideal for rapid prototyping and smaller projects. VHDl syntax is more complex and is hard to grasp initially. The development time is longer due to its strongly typed system. It is ideal for large complex systems that need better documentation facilitated by the verbosity in VDHL. It provides better control over the project and is useful in mission-critical systems such as aerospace and defence.

- Simulation and verification: Verilog is preferred in simulation due to its concise and easy-to-understand syntax. It is compatible with various simulation environments and is easy to run simulations for smaller designs. VDHL is rigid in structure and its strong typing allows for better error checking and debugging. This makes it suitable for larger designs requiring precise timing behaviour. Often, it is chosen for high-performance designs where simulation and verification are critical.

- Design abstraction level: Verilog offers a more hardware-oriented approach with simpler constructs for specifying the hardware behaviour. Designs using straightforward logic and fast simulation prefer using Verilog. VHDL provides more flexibility and is commonly used in environments needing a formal and detailed specification. This makes it viable for large systems and systems requiring strict timing analysis and verification. The type-checking is strong and provides more flexibility in expressing complex designs.

- Portability and compatibility: Verilog is compatible with a wide range of tools, thus making it ideal for a cross-platform or crosstool design. Designers and people with programming languages can use it to work across different tools with minimal adaptation. VDHL is highly portable and works well across various platforms. However, its verbosity makes it more difficult to port between tools. This complexity hinders it from being modified for use in different environments. When there is a need for a detailed description, VDHL is the ideal choice. Portability and compatibility between different design tools and platforms are significant factors in choosing the right HDL for your project.

Choosing the right HDL for your project depends on several factors such as project complexity and design specifications. Besides, the industry standards and team expertise contribute to the choice of HDL.

Conclusion: It can be rightly concluded that both Verilog and VHDL are imperative tools in VLSI design as each has its unique strengths and capabilities depending upon the project’s needs. The choice of HDL should be based on factors such as project complexity and industry requirements along with team expertise and specific design goals. Choosing the right language depends on several factors and gives different results. Hence the choice should be made prudently so that the needs of the required project are met. If the company provides rigorous design specifications and detailed documentation, the choice of VHDL is ideal as it is known for its strong typing and more verbose nature. However, if the company is looking for simplicity and ease of use is more hardware-centric in its approach, and is running short of time for project development, the Verilog language is more suitable. By understanding the strengths and weaknesses of each language, the designers can make an informed decision ensuring the success of their VSLI project. The industry of semiconductor engineering in usa is deeply involved in designing and programming critical designs for various industries. The use of semiconductors to power electronics and medical devices is based on the efficient working of these devices for the seamless flow of information and access to data. So check the project’s scope and industry standards along with team expertise to select the hardware description language and meet the project requirements.